vivado中如何查看各个模块的资源利用率

本文分析了FPGA设计中各模块的资源利用率情况,重点介绍了LUT与LUTRAM的区别,并详细说明了12种关键资源的功能特性。资源报告显示,顶层模块整体利用率较低,其中hdmi_color_bar模块为主要资源消耗者。文章特别解释了BlockRAM出现小数计数的原因,并区分了LUT作为逻辑和存储时的不同应用场景。随后系统性地阐述了包括SliceLUTs、SliceRegisters、BlockRAM

目录

1.各个模块的资源利用率

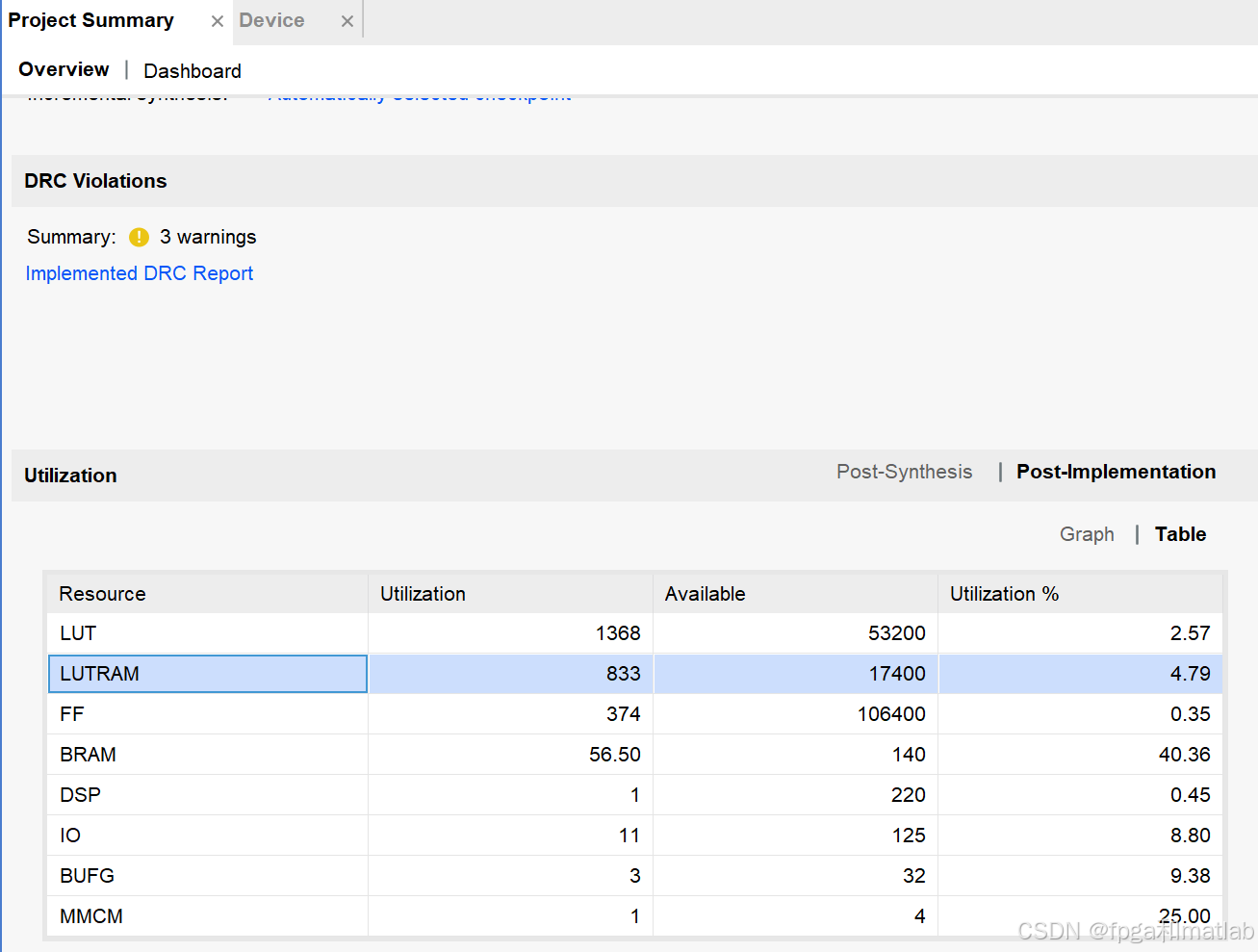

首先在完成工程的综合布局之后,首先可以看到如下的资源列表:

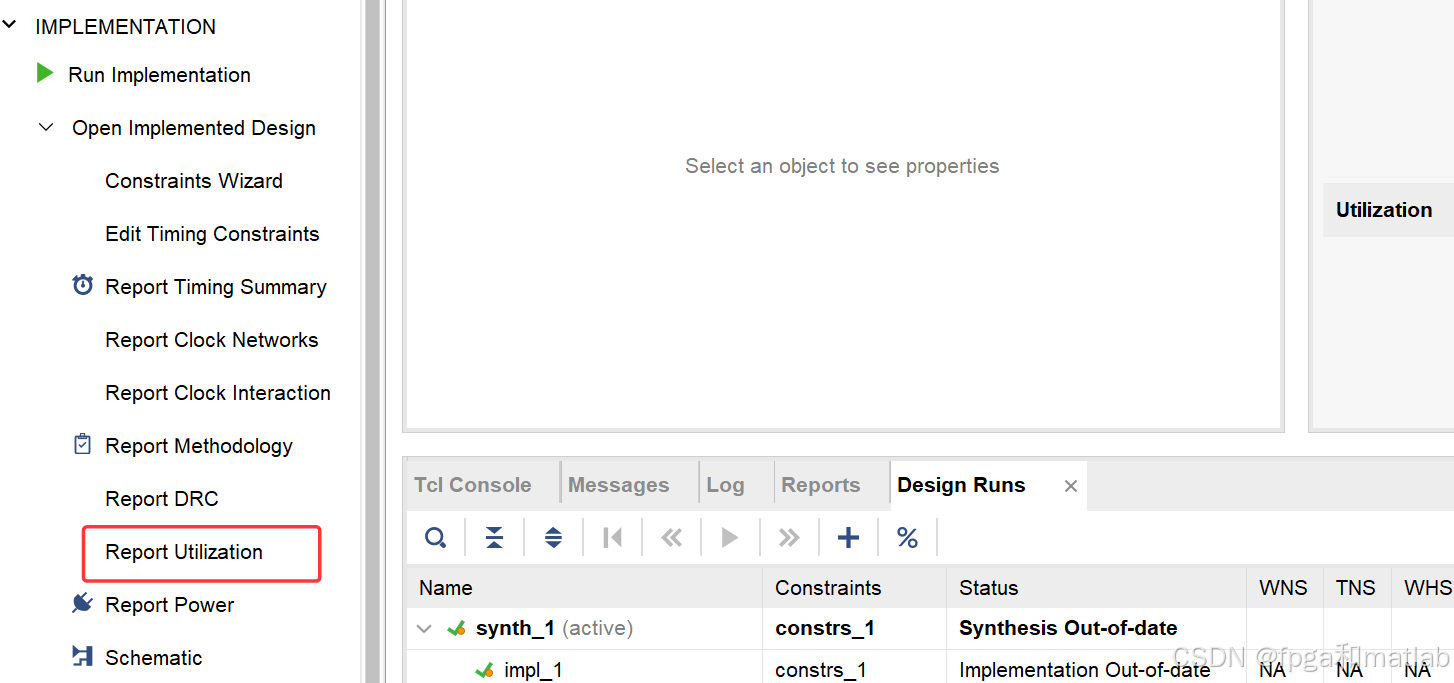

然后我们点击如下的按键,打开系统的各个模块的资源利用率:

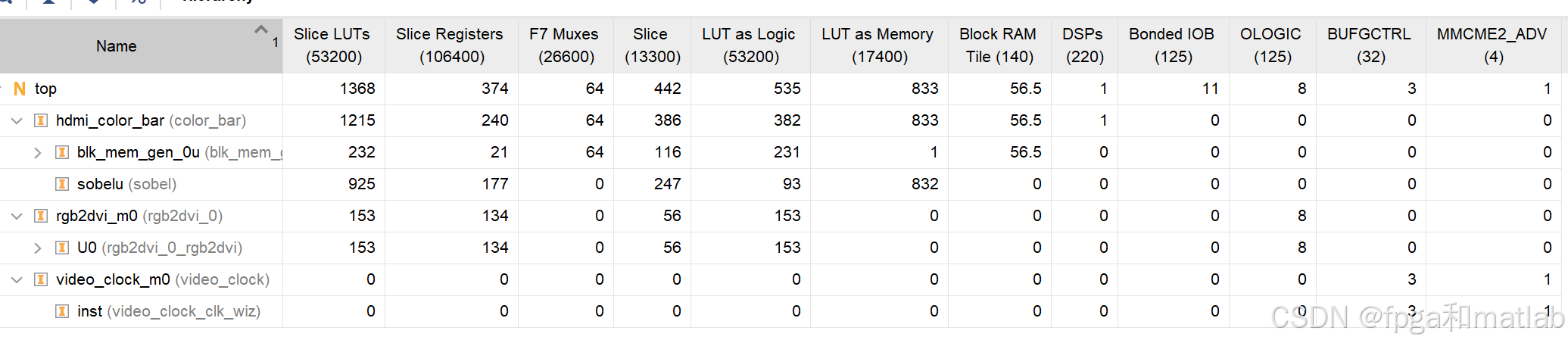

点击之后,可以看到如下的内容:

从上面的内容可知:

顶层模块(top)资源总消耗

Slice LUTs:1368(总容量53200)

Slice Registers:374(总容量106400)

Block RAM Tile:56.5(总容量140)

DSPs:1(总容量220)

可以看出整体资源利用率较低,还有较大余量

主要子模块资源消耗

hdmi_color_bar模块:是资源消耗的主要模块,消耗了1215个SliceLUTs和全部的Block RAM(56.5)

其中blk_mem_gen_0子模块消耗了232 个Slice LUTs

sobelu子模块消耗了925个Slice LUTs和832个用作内存的LUT(LUT as Memory)

rgb2dvi_m0模块:主要消耗了153个Slice LUTs和8个Bonded IOB

video_clock_m0模块:未消耗LUT和寄存器资源,仅使用了3个BUFGCTRL和1个MMCM2_ADV(时钟管理资源)

Block RAM小数的解释

报告中Block RAM Tile出现了56.5这样的小数,这与之前提到的原因一致:FPGA的Block RAM通常以36Kb为单位,而每个36Kb Block RAM可拆分为两个18Kb的Block RAM,当设计中使用了 18Kb的Block RAM时,就会出现0.5的计数。

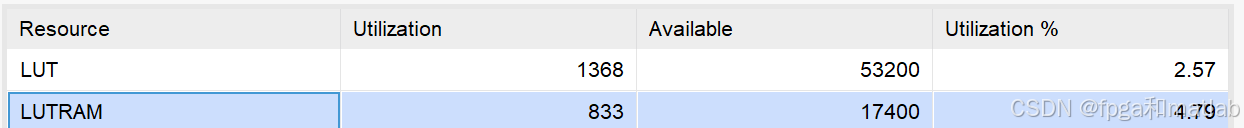

2.LUT和LUTRAM的区别

LUTRAM:将LUT用作分布式RAM/ROM(SLICEM中的LUT),包含移位寄存器(SRL)。

验证实验:设计包含3个模块:5bit计数器(消耗1个LUT)、32×1分布式RAM(消耗1个SLICEM 中的LUT)、32位移位寄存器(消耗1个SLICEM中的LUT)。通过OOC综合、查看布线后DCP文件的report_utilization报告,结果为:消耗1368个LUT、833个LUTRAM。

3.各个资源的功能简介

1. Slice LUTs(Slice查找表)

Slice Look-Up Tables,FPGA中最基础的逻辑单元,可实现组合逻辑(如与、或、非、多路选择器等),也可配置为分布式RAM/ROM、移位寄存器(SRL)。(53200)表示当前FPGA芯片总共包含53200个Slice LUT资源。

2. Slice Registers(Slice寄存器)

通常是D触发器,用于存储数据、实现时序逻辑(如计数器、状态机、寄存器组等)。(106400) 表示芯片总共有106400个Slice寄存器。

3. F7 Muxes(F7多路选择器)

Function 7 Multiplexers,FPGA Slice内部的专用多路选择器,用于高效实现更复杂的逻辑(如6输入以上的组合逻辑),是LUT的辅助逻辑资源。(26600) 表示芯片总共有26600个F7 Mux资源。

4. Slice(逻辑切片)

FPGA的基本“逻辑单元组”,通常包含若干LUT、寄存器、F7/F8 Mux等资源。整个FPGA由大量Slice阵列组成。(13300)表示芯片总共有13300个Slice资源。

5. LUT as Logic(用作逻辑的LUT)

专门统计被配置为“组合逻辑/时序逻辑”的LUT数量(区别于用作存储的LUT)。(53200)对应芯片LUT的总容量(与Slice LUTs总数一致)。

6. LUT as Memory(用作存储的LUT)

统计被配置为“分布式RAM/ROM/移位寄存器(SRL)” 的LUT数量(LUT可复用为小型存储资源)。(17400)表示芯片中LUT可复用为存储的最大容量。

7. Block RAM Tile(块RAM)

Block RAM即Block Random Access Memory Tile,FPGA中的专用大容量存储资源,通常以“Tile”为单位(比如一个Tile对应36Kb容量),用于实现较大的RAM、ROM、FIFO等存储结构。(140)表示芯片总共有140个Block RAM Tile资源。出现小数(如之前的56.5)是因为1个36Kb Tile可拆分为 2个18Kb Tile,使用18Kb时会统计为0.5个Tile。

8. DSPs(数字信号处理单元)

DSPs为Digital Signal Processing Slices,专用的算术运算单元,可高效实现乘法、乘加、累加等运算,常用于数字信号处理、图像处理、算法加速等场景。(220)表示芯片总共有220个DSP资源。

9. Bonded IOB(键合I/O缓冲器)

Bonded IOB为Bonded Input/Output Buffer,FPGA与外部设备通信的I/O接口资源,负责信号的输入/输出驱动、电平转换、阻抗匹配等。(125)表示芯片总共有125个Bonded IOB资源。

10. OLOGIC(输出逻辑单元)

IOB中的专用输出逻辑模块,辅助实现输出信号的时序控制、电平调整等功能。(125)表示芯片总共有125个OLOGIC资源。

11. BUFGCTRL(全局时钟缓冲器)

BUFGCTRL为Global Clock Buffer Control。BUFGCTRL是FPGA 中的全局时钟资源,用于驱动高速、低抖动的全局时钟信号,确保时钟在芯片内的同步性。(32) 表示芯片总共有32个BUFGCTRL 资源。

12. MMCME2_ADV(高级时钟管理单元)

MMCME2_ADV为Mixed-Mode Clock Manager Enhanced 2 Advanced。MMCME2_ADV是FPGA的时钟管理模块,用于实现时钟的分频、倍频、相位调整、抖动抑制等功能,是系统时钟方案的核心资源。其中(4)表示芯片总共有4个MMCME2_ADV资源。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献12条内容

已为社区贡献12条内容

所有评论(0)