FPGA时序约束分析20——多周期路径约束分析

本文介绍了FPGA时序约束中的多周期路径约束方法,主要包含四种场景:1. 同频同相多周期路径约束,适用于门控时钟等需多周期传输数据的电路;2. 同频异相多周期路径约束,适用于PLL移相等时钟同频不同相的情况;3. 慢时钟到快时钟域约束;4. 快时钟到慢时钟域约束。通过set_multicycle_path命令设置建立时间和保持时间的周期数,可调整时序分析工具默认的单周期检查规则,使其匹配实际电路需

目录

在FPGA时序约束中,多周期路径约束是处理特殊时序逻辑的重要手段,用于调整时序分析工具默认的单周期时序检查规则,以匹配实际电路的多周期数据传输需求。

1.多周期路径约束语法

多周期路径约束通过set_multicycle_path命令实现,其基本语法结构如下:

set_multicycle_path [-setup] [-hold] [-rise] [-fall] [-start] [-end] [-reset_path] [-from <args>] [-to <args>] [-through <args>] <path_multiplier>参数说明

-setup / -hold:指定约束作用于建立时间(Setup)还是保持时间(Hold)。

-start / -end:指定参考时钟是源时钟(-start)还是目标时钟(-end)。默认以源时钟为参考。

<path_multiplier>:多周期值,需为大于 0 的整数,默认建立时间周期数为 1,保持时间为 0。

-from / -to / -through:指定路径的起点、终点或中间节点,可通过

get_cells、get_pins等命令选取目标单元或引脚。

2.同频同相多周期路径约束

同频同相的多周期路径有两种不同的结构:一种是源时钟和目标时钟共享同一个时钟源;另一种是源时钟和目标时钟使用独立的时钟源,但在创建时钟时,设置了相同的频率和相位。这两种结构在多周期路径约束的应用上是完全一致的。

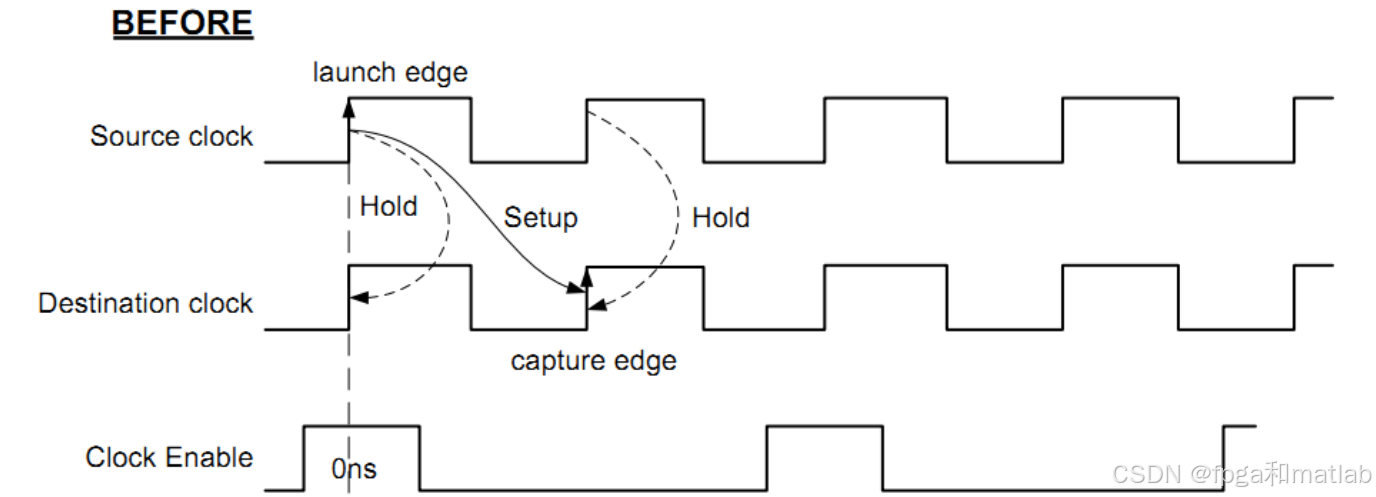

如上图所示,当源时钟和目标时钟频率相同、相位一致,但数据传输需多个周期时,需设置同频同相多周期路径约束。以门控时钟降频电路为例,数据需2个时钟周期完成传输,保持时间要求与默认一致。其基本语法结构如下:

# 建立时间约束:多周期值为2,指定路径从FF1到FF2

set_multicycle_path 2 -setup -from [get_cells FF1] -to [get_cells FF2]

# 保持时间约束:多周期值为1,修正保持时间分析

set_multicycle_path 1 -hold -from [get_cells FF1] -to [get_cells FF2]setup=2表示建立时间分析的周期数为2,即数据在第2个时钟沿被捕获。

hold=1用于修正保持时间分析,避免因建立时间约束导致保持时间检查过度宽松。

3.同频异相多周期路径约束

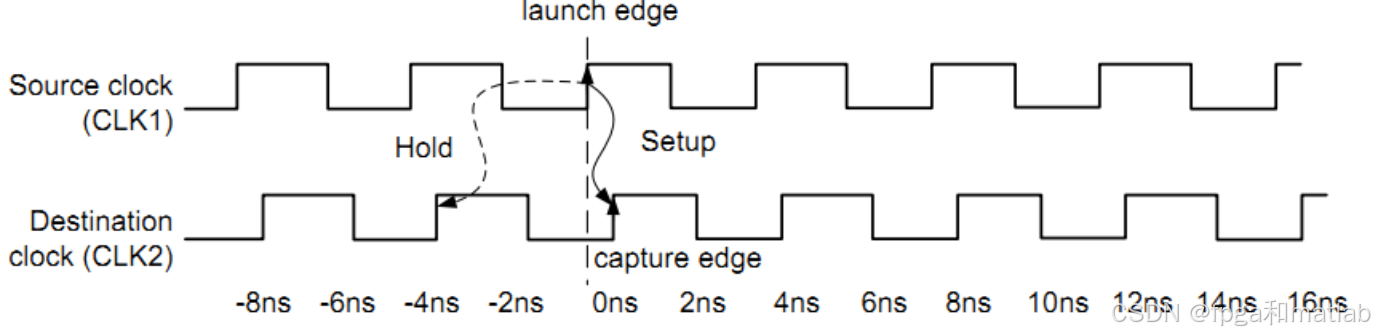

如上图所示,源时钟和目标时钟频率相同但相位不同时,需明确相位差异对时序的影响。以PLL移相电路为例,源时钟经PLL移相 72°(2ns),需调整多周期约束以匹配实际时序。

# 建立时间约束:多周期值为2,指定路径从FF1到FF2

set_multicycle_path 2 -setup -from [get_cells FF1] -to [get_cells FF2]由于时钟同频异相,仅需设置建立时间的多周期约束(

setup=2),即可自动调整保持时间分析,使建立时间和保持时间的时序检查更合理。

4.不同频多周期路径约束

当源时钟和目标时钟频率不同时,需区分“慢时钟到快时钟域”和“快时域到慢时钟域”两种场景。

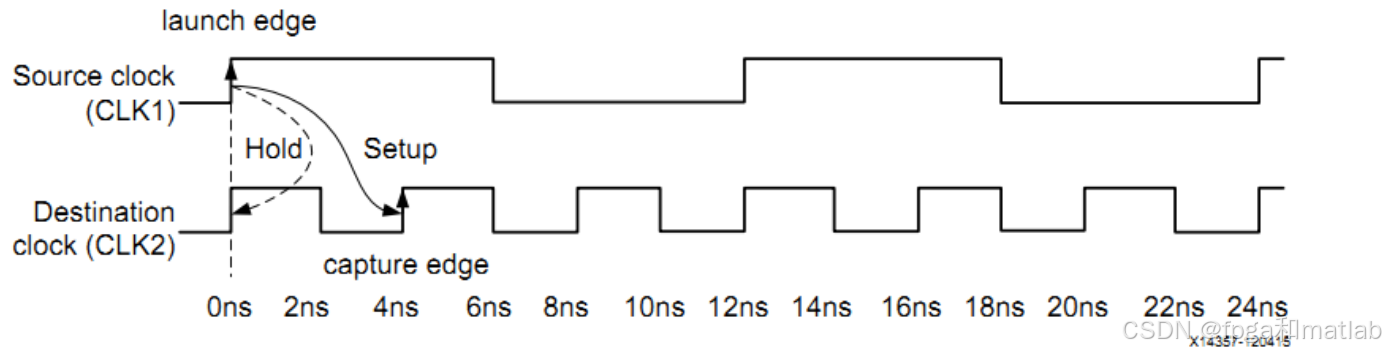

4.1 慢时钟域到快时钟域

源时钟频率低,目标时钟频率高,数据需多个目标时钟周期传输。以慢时钟(clk_slow)到快时钟(clk_fast,频率为clk_slow的3倍)为例。

# 建立时间约束:多周期值为3,指定目标时钟(-end)

set_multicycle_path 3 -setup -end -from [get_pins FF1/C] -to [get_pins FF2/D]

# 保持时间约束:多周期值为2,修正保持时间分析

set_multicycle_path 2 -hold -end -from [get_pins FF1/C] -to [get_pins FF2/D]-end参数指定调整目标时钟(快时钟),setup=3表示建立时间分析的周期数为3。

hold=2 用于修正保持时间,使其恢复到实际需求的检查规则。

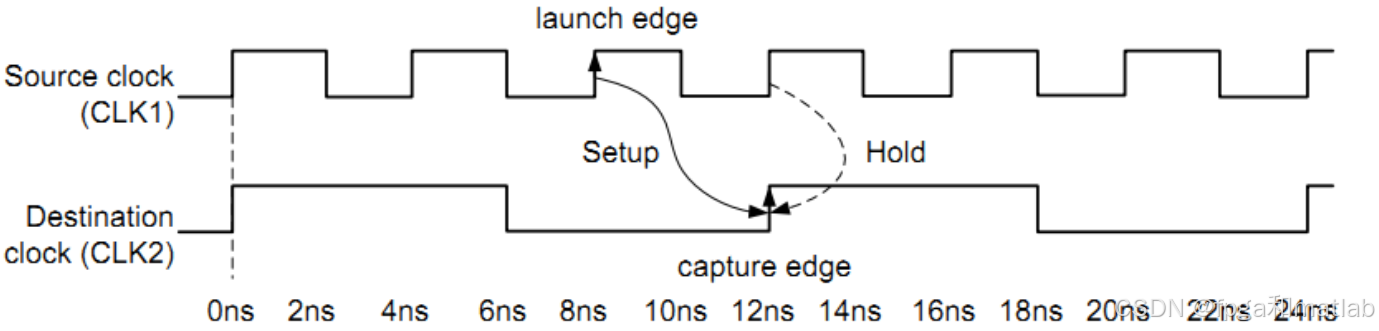

4.2 快时钟域到慢时钟域

源时钟频率高,目标时钟频率低,目标时钟需等待多个源时钟周期捕获数据。以快时钟(clk_fast,频率为clk_slow的3倍)到慢时钟(clk_slow)为例。

# 建立时间约束:多周期值为3,指定源时钟(-start)

set_multicycle_path 3 -setup -start -from [get_cells FF1] -to [get_cells FF2]

# 保持时间约束:多周期值为2,修正保持时间分析

set_multicycle_path 2 -hold -start -from [get_cells FF1] -to [get_cells FF2]-start 参数指定调整源时钟(快时钟),setup=3表示建立时间分析中源时钟的周期数为3。

hold=2用于修正保持时间,使其符合实际电路的保持需求。

火山引擎开发者社区是火山引擎打造的AI技术生态平台,聚焦Agent与大模型开发,提供豆包系列模型(图像/视频/视觉)、智能分析与会话工具,并配套评测集、动手实验室及行业案例库。社区通过技术沙龙、挑战赛等活动促进开发者成长,新用户可领50万Tokens权益,助力构建智能应用。

更多推荐

已为社区贡献38条内容

已为社区贡献38条内容

所有评论(0)